А где вообще Intel? Только что еле-еле переползли на 10 нм?

Мы решили узнать, что измеряют эти нанометры? И так ли важно ими мериться или это просто маркетинг? И реально ли Intel так безбожно устарел?

Прежде чем перейти к процессорам в наших смартфонах и компьютерах, немного основ как устроен процессор?

Знакомьтесь это транзистор! Ключевой элемент всех процессоров. Фактически транзистор это переключатель. Ток течет через него это 1, ток не течет это 0. Это и позволяет считать в двоичной системе основа всех процессоров!

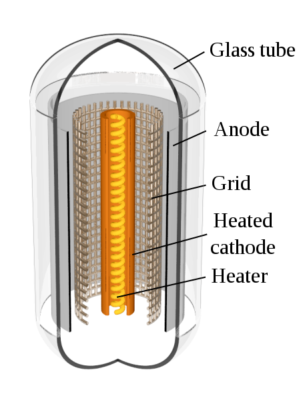

Раньше транзисторами были вакуумные лампочки. Условно горит или не горит: единица или ноль.

Таких лампочек нужно было очень много, чтобы всё как-то работало. Например, компьютер ENIAC 1946 года, который участвовал в создании водородной бомбы насчитывал 17,5 тысяч вакуумных ламп и весил 27 Тонн, занимая 167 квадратных метров. При этом он жрал 150кВт электричества.

И тут один из ключевых моментов, на который стоит обратить внимание. Еще раз повторю энергопотребление у этих 17,5 тысяч лампочек составляло 150 кВт.

Но в начале 1960-х случилась революция изобретение и начало производства полевых транзисторов.Как раз у них исходным полупроводником является кремний отсюда и всем известная силиконовая, кхм, тоесть Кремниевая долина!

И тут понеслось! Размеры транзисторов уменьшились настолько, что они стали потреблять существенно меньше электричества и занимать меньше места. И количество транзисторов в вычислительной технике начало увеличиваться с огромной скоростью! А вместе с ним и мощность вычислительных систем!

В первом промышленном процессоре Intel 4004, который был выпущен в 1971 году было 2250 транзисторов.

А сейчас например в A13 Bionic этих транзисторов 8.5 миллиардов это больше чем людей на планете! Ну пока

Но на сколько вообще уменьшились современные транзисторы, насколько они маленькие? Простое сравнение легкое для понимания например, с человеческим волосом!

На его срезе можно разместить почти 1.5 миллиона современных транзисторов сделанных по 7-нанометровому техпроцессу!

То есть у вас на толщине человеческого волосе можно разместить в 4 раза больше транзисторов, чем было в процессоре Intel 4004!

Почему же надо уменьшать? Тут все более-менее очевидно!

Во-первых, чем меньше транзистор тем меньше он потребляет энергии. Вы уже это поняли на примере ламповых.

А во-вторых их больше помещается на кристалле, а значит растёт производительность. Двойная выгода!

И тут мы переходим к понятию техпроцесса или Technology Node что же это такое?

Если максимально упростить, то значением техпроцесса исторически являлась минимальная длина канала транзистора как видно на картинке не стоит его путать с размерами транзистора целиком.

То есть, чем меньше размер техпроцесса тем лучше это нам и пытаются донести компании, но так ли всё просто?

И тут важно другое: транзисторы бывают разные и они отличаются не только по размеру, но и по своей структуре.

Классические, планарные или плоские, транзисторы перестали использоваться относительно недавно в 2012 году. Они уступили место трёхмерным транзисторам, где вытянули канал в третье измерение, уменьшив его толщину и тем самым уменьшив сам транзистор.Такаяструктура называется FinFET они и используются сейчас.

Данная технология очень помогла уменьшить размер транзисторов и главное сильно повысила количество транзисторов на единицу площади, что и является одним из ключевых показателей для производительности!

Но означает ли сегодня понятие техпроцесс тоже самое, что и несколько лет назад?

Во всей индустрии прослеживалась очень важная тенденция каждый следующий техпроцесс был меньше предыдущего на 30%, что помогало удвоить количество транзисторов при сохранение того же энергопотребления например 130*0.7=90 нм, 90*0.7=65 нм, далее до 45 нм, 32 нм, и так далее.

И это пока соответствует Закону Мура:

Количество транзисторов, размещаемых на кристалле интегральной схемы, удваивается каждые 24 месяца.

Что же стоит за этой игрой чисел?

Мы уже выяснили, что техпроцесс это размер затвора транзистора, то есть длина канала, который пропускает или не пропускает через себя ток и этот размер ключевой!

Но оказывается это истинно, только если мы говорим о старых 32 нм там все точно, хоть линейкой измеряй! И этот параметр был закреплен документально!

Но так было до 2009 года, когда из так называемого Международного плана по развитию полупроводниковой технологии было исключено понятие техпроцесса и его обозначения!

Простым языком цифры указанные в тех процессе сегодня это просто маркетинговый лейбл!

Производители пошли вразнос и начали называть всё подряд 10, 7 и вообще 5 нанометрами, а кто-то уже говорит и о 3 нанометрах! Можно всё это ставить в кавычки, как простое обозначение поколения процессоров!

Вот вам например структура процессора Apple A12, произведенного на заводе TSMC по 7- нанометровому техпроцессу. Обратите внимание на шкалу масштаба в левом нижнем углу.

Если сравнить масштаб и посчитать, то получается, что ширина канала 8 нанометров, при том, что официально процесс называется 7-нанометровым.

Теперь давайте сравним 10-нанометровый процесс у Intel и 7-нанометровый у TSMC.

Кстати, знайте, что сегодня TSMC это компания, которая производит процессоры для AMD, а также делает Apple A13 и Snapdragon 865 поэтому считайте, что мы сравниваем сразу все их чипы.

Обратите внимание на размерность. Сразу видно, что те же 10нм у Intel почти такие же как 7 нанометров у TSMC! Так что выходит Intel не так уж отстали от AMD и других производителей они просто проиграли маркетинговую битву? Тут тоже все не так однозначно!

Внезапно по некоторым параметрам Intel даже выигрывают у TSMC.

Смотрите на 1 квадратный миллиметр 10нм кристалла Intel помещается примерно на 5 процентов больше транзисторов, чем на 7нм у того же Apple, Qualcomm или AMD.

Но при этом у повышенной плотности есть и минусы увеличенный нагрев!

Значит получается что кристаллы Intel мощнее, но за счет плотности они больше греются. Таким образом, мы получаем тот самый пресловутый троттлинг.

А процессоры производства TSMC Apple Qualcomm и AMD выигрывают именно за счет более просторного расположения транзисторов примерно тех же размеров.

Как они это делают это скорее вопрос внутренней архитектуры, а не цифека, которая стоит в названии тех процесса.

Не думайте, что я забыл про архитектуру N7FF+ да она еще плотнее чем у Intel, но если говорить о чипах серия AMD Zen 2, Applу A13, Snapdragon 865 все сделаны на основе TSMC 7FF и она проигрывает в плотностиIntel.

Единственный процессор, который уже производится по новой технологии N7FF+ с использованием экстремальной УФ-литографии это Kirin 990 5G. Тут конечно плотность транзисторов сильно возрастает аж на 15 процентов!

По идее производители просто идут по немного разному пути и если заглянуть в будущее, то становится понятно по какому: вот вам табличка того как все будет чипы следующего поколения.

Нас интересует строчка про плотность транзисторов на 1 квадратный миллиметр!

По этим данным Intel более чем на 30 процентов обходит и Samsung, и TSMC в плотности транзисторов и это при том, что тут мы сравниваем уже 7 нм у одного производителя и 5 у другого.

Откуда такой прирост? Как возможно такое повышение плотности процы просто будут взрываться или работать только с навороченными система охлаждения?

Не совсем так. Все дело в том, что Intel планирует перейти на транзисторы совершенно другой структуры под названием HNS Horizontal Nano Sheets это и позволит сделать скачок!

Но похожие планы есть и у Samsung они идут немного в другую сторону к структуре Gate-All-Around FET.

Вот как это выглядит в реальности не так симпатично, но вы только подумайте о том, какие они маленькие!

В итоге мы поняли, что за маркетинговыми названиями 7 нм и 5 нм скрывается битва архитектур, а в будущем мы сможем выяснить чей же путь был верным.

Что можно сказать абсолютно точно нас ждёт огромный скачок среди всех чипов как мобильных так и десктопных уже в течение ближайших нескольких лет.

На этой ноте не хочется заканчивать тему процессоров, ведь мы изучили немало информации и документов, в том числе разобрались в процессе производства. Например, вы слышали о таком процессе Экстремальная Ультрафиолетовая Литография?Если на пальцах, это какая-то фантастика капля олова превращается в плазму после попадания лазера: именно так создаются современные процессоры. Но сами установки может создавать только одна компания в мире и все гиганты от нее зависят.